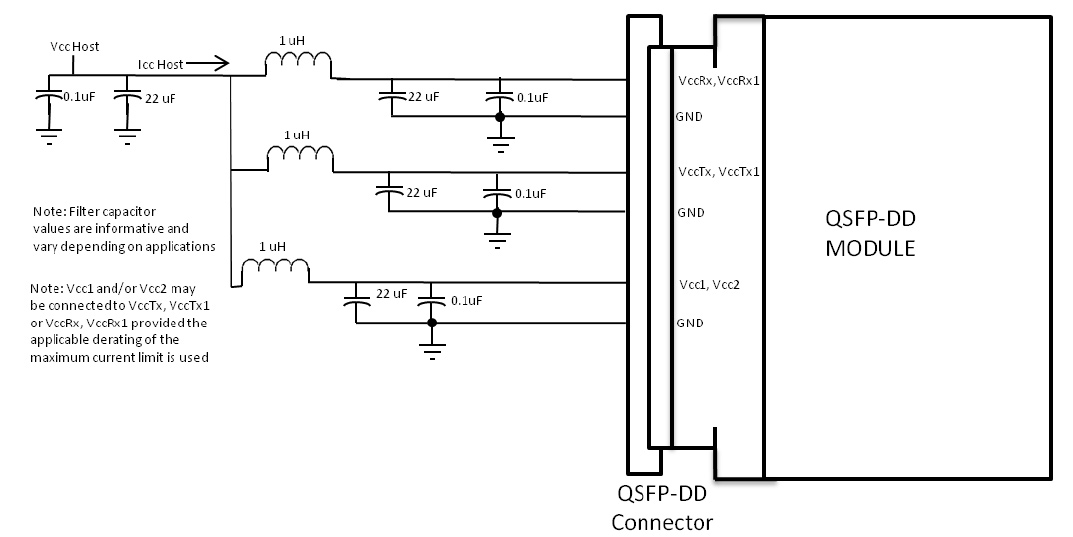

El transceptor 2x100GBASE-SR4 QSFPDD es un tipo de transceptor paralelo, el paquete de matriz VCSEL y PIN es la técnica clave, a través del sistema I2C puede contactar con el módulo. Es un QSFP de ocho canales, enchufable, paralelo, fibra óptica de doble densidad para 2 aplicaciones 100 Gigabit Ethernet, módulo de alto rendimiento para aplicaciones de interconexión y comunicación de datos de varios carriles de corto alcance. Integra ocho carriles de datos en cada dirección con un ancho de banda de 8x25,78125 Gbps. Cada carril puede operar a 25,78125 Gbps hasta 70 m usando fibra OM3 o 100 M usando fibra OM4. Estos módulos están diseñados para operar en sistemas de fibra multimodo utilizando una longitud de onda nominal de 850nm. La interfaz eléctrica utiliza un conector de tipo de borde de contacto 76. La interfaz óptica utiliza un conector MTP de 24 fibras (MPO). Este módulo incorpora circuito probado y tecnología VCSEL para proporcionar una larga vida útil confiable, un alto rendimiento y un servicio constante.

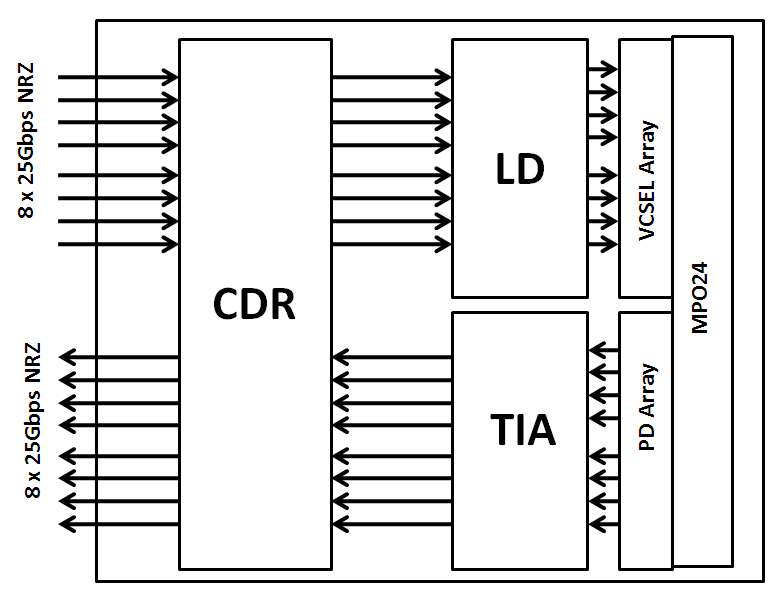

Figura 1. Diagrama de bloque de módulo

Características

● 8 canales módulos transceptores full-duplex

● Velocidad de transmisión de datos de hasta 26Gbps por canal

● 8 canales 850nm VCSEL array

● 8 canales PIN foto detector de matriz

● Circuitos CDR internos en canales receptores y transmisores

● Soporte de bypass CDR

● Bajo consumo de energía <4W

● Factor de forma DD QSFP conectable en caliente

● Longitud máxima de enlace de 70m en fibra multimodo OM3 (MMF) y 100m en OM4 MMF

● Receptáculo conector MPO24

● Temperatura del caso de funcionamiento 0 °C a 70 °C

● Tensión de fuente de alimentación 3,3 V

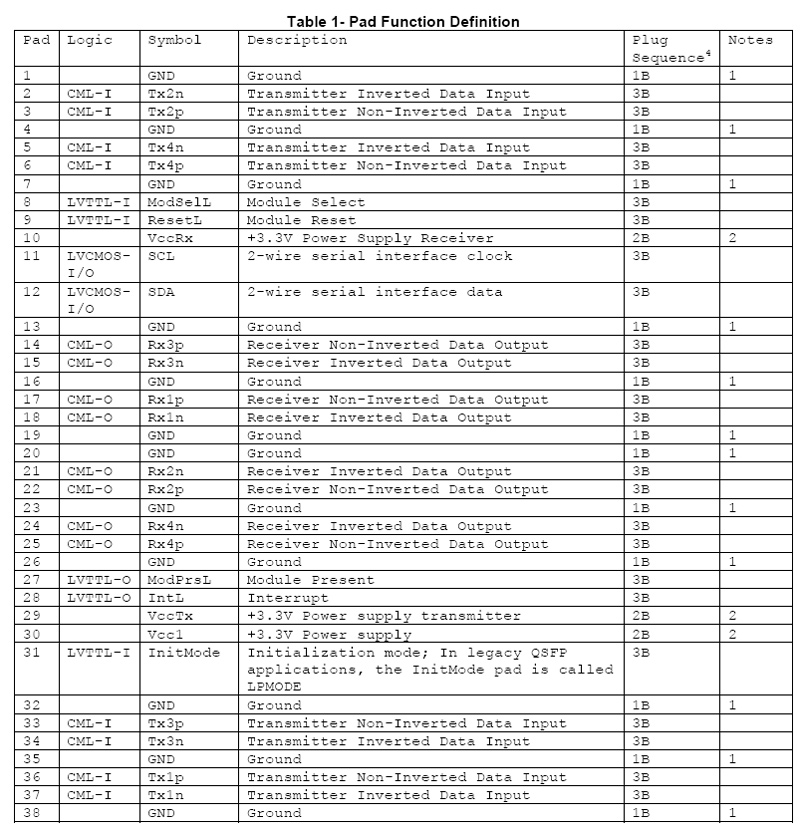

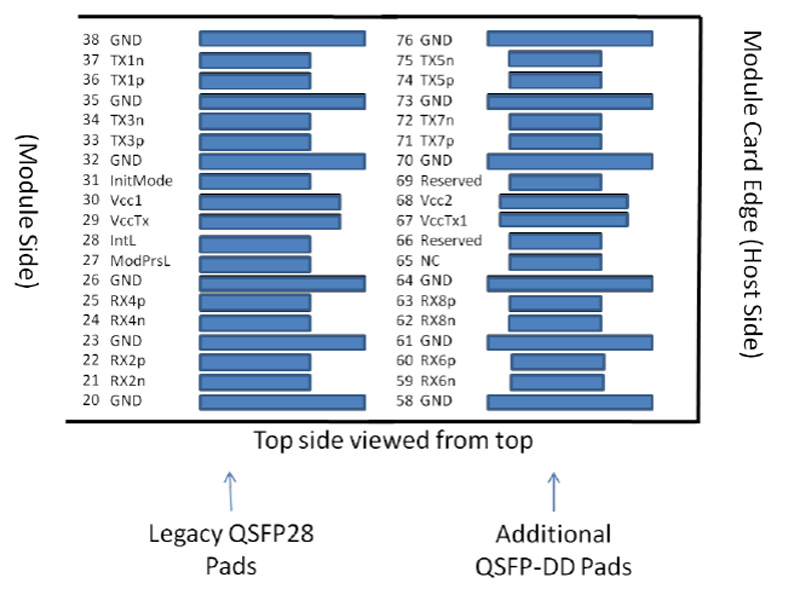

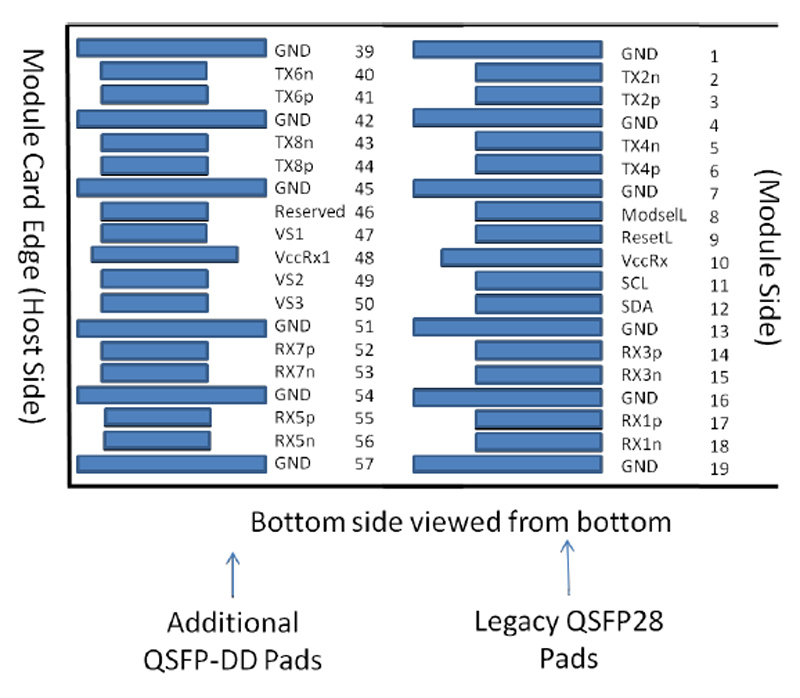

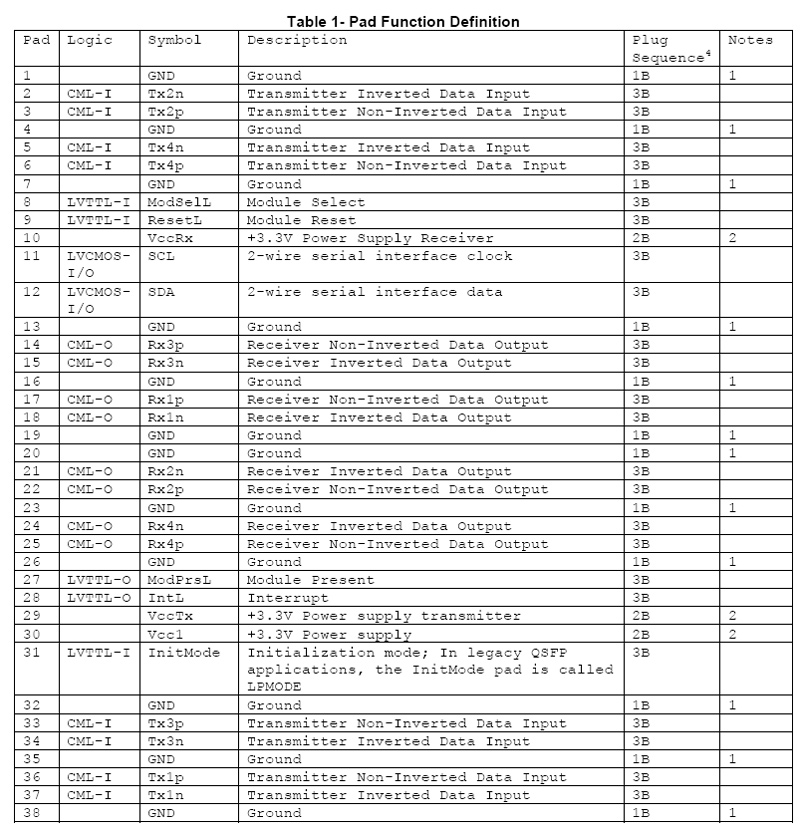

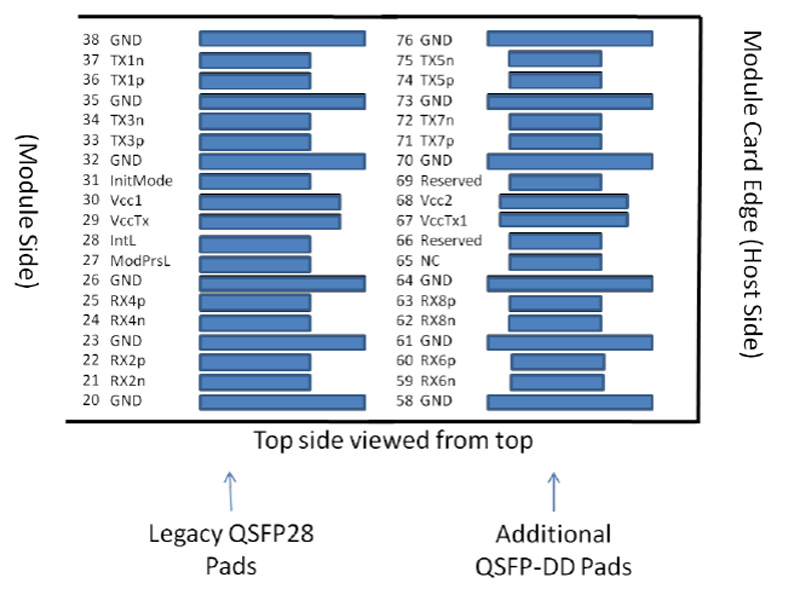

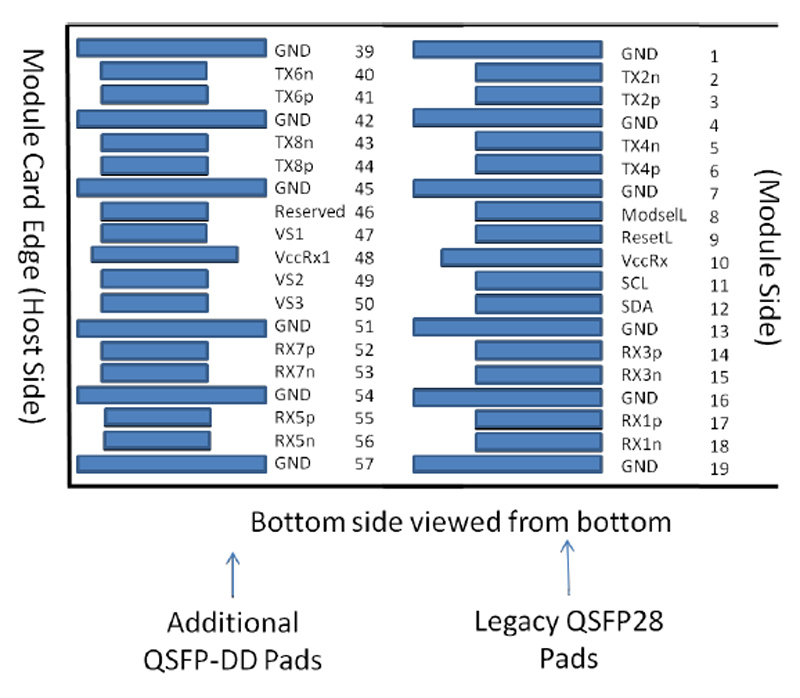

Pin Deion

Figura 2. Detalles de la salida eléctrica

Pin ModSelL

El ModSelL es una señal de entrada que se debe tirar a Vcc en el módulo de QSFP-DD. Cuando el host lo mantiene bajo, el módulo responde a comandos de comunicación en serie de 2 cables. El ModSelL permite el uso de múltiples módulos de QSFP-DD en un único bus de interfaz de 2 cables. Cuando ModSelL es "Alto", el módulo no responderá ni reconocerá ninguna comunicación de interfaz de 2 cables desde el host.

Para evitar conflictos, el sistema host no intentará las comunicaciones de interfaz de 2 cables dentro del tiempo de desafirmación ModSelL después de que se escrituren los módulos de QSFP-DD. De manera similar, el host debe esperar al menos durante el período de tiempo de afirmación de ModSelL antes de comunicarse con el módulo recién formado. Los períodos de afirmación y desafirmación de diferentes módulos pueden superponerse siempre que se cumplan los requisitos de tiempo anteriores.

Pin ResetL

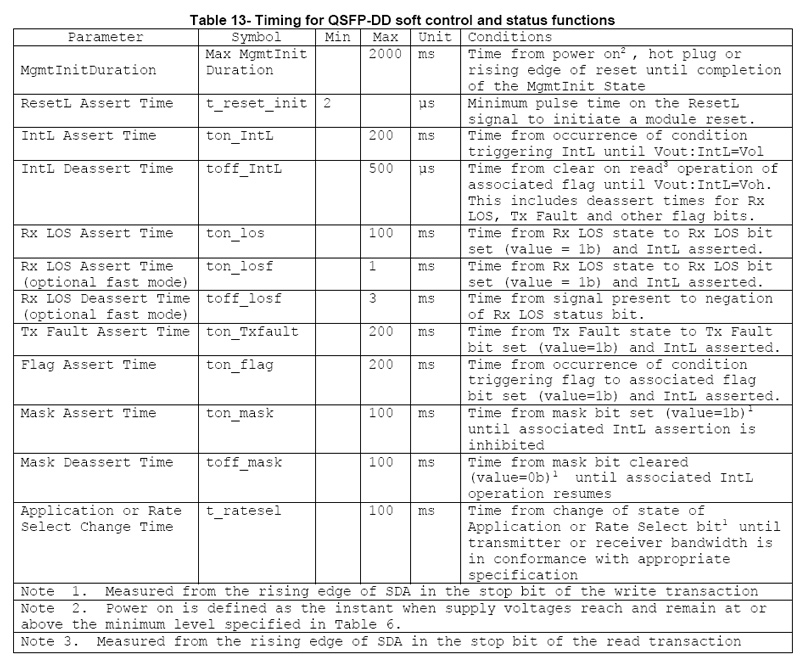

La señal ResetL se llevará a Vcc en el módulo. Un nivel bajo en la señal de ResetL durante más tiempo que la longitud mínima del pulso (t_Reset_init) (consulte la Tabla 13) inicia un restablecimiento completo del módulo, devolviendo todos los ajustes del módulo de usuario a su estado predeterminado.

Pin de InitMode

InitMode es una señal de entrada. La señal de InitMode se debe subir a Vcc en el módulo de QSFP-DD. La señal InitMode permite que el host defina si el módulo QSFP-DD se inicializará bajo el control de software del host (InitMode afirmó High) o el control de hardware del módulo (InitMode desafirmó Low). Bajo el control del software del host, el módulo permanecerá en el modo de baja potencia hasta que el software permita la transición al modo de alta potencia, como se define en la sección 7,5. Bajo el control de hardware (InitMode de-afirmó Low), el módulo puede pasar inmediatamente al modo de alta potencia después de que se inicialice la interfaz de gestión. El host no cambiará el estado de esta señal mientras el módulo esté presente. En aplicaciones QSFP heredadas, esta señal se denomina LPMode. Consulte SFF-8679 para ver la señal deion.

Pin ModPrsL

ModPrsL debe ser retirado a Vcc Host en la placa host y conectado a tierra en el módulo. El ModPrsL se afirma como "Bajo" cuando el módulo es Ed y desafirma "Alto" cuando el módulo está físicamente ausente del conector host.

Pin IntL

IntL es una señal de salida. La señal IntL es una salida de colector abierta y debe tirarse a Vcc Host en la placa host. Cuando la señal IntL se afirma baja, indica un cambio en el estado del módulo, una posible falla operativa del módulo o un estado crítico para el sistema host. El host identifica la fuente de la interrupción utilizando la interfaz serie de 2 cables. La señal IntL se desafirma como "Alta" después de que se leen todas las banderas de interrupción establecidas.

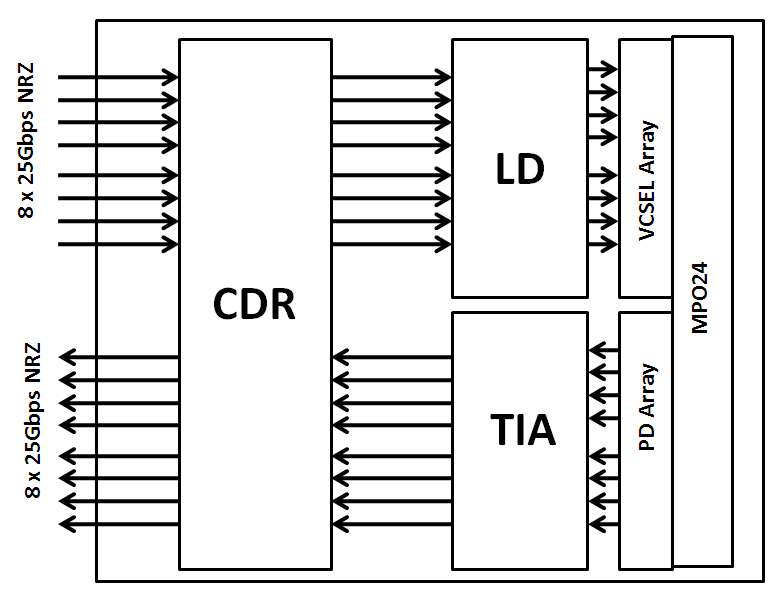

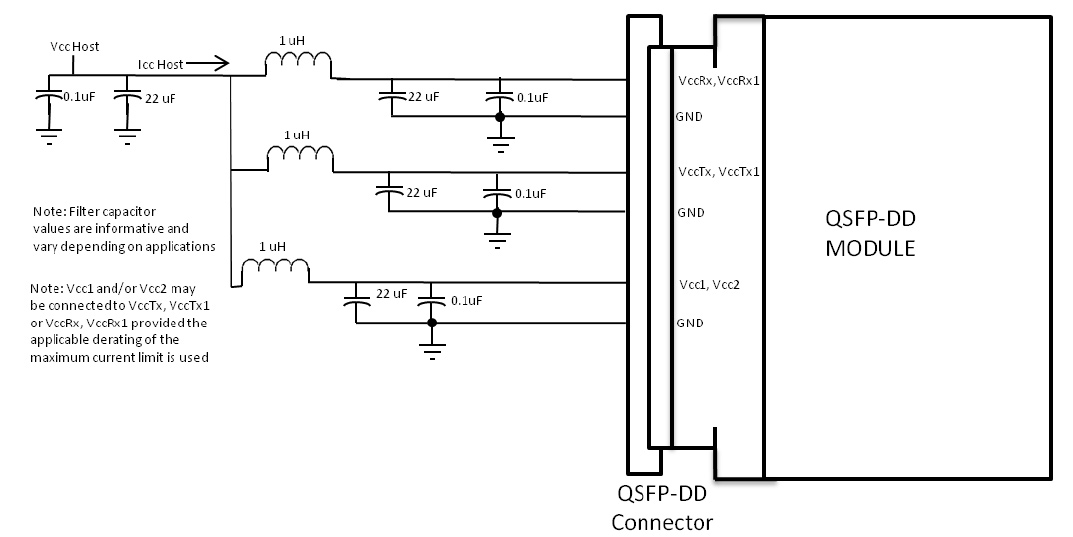

Filtrado de fuente de alimentación

La placa central debe utilizar el filtrado de la fuente de alimentación que se muestra en la Figura 3.

Figura 3. Filtrado de fuente de alimentación de la placa host

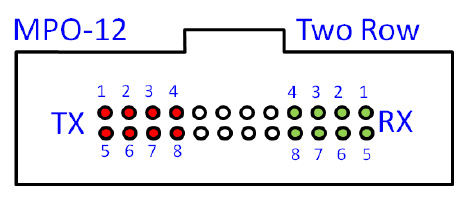

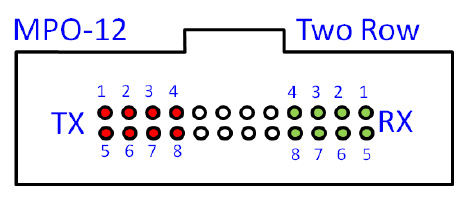

Lanes de interfaz óptica y asignación

El puerto de interfaz óptica es un conector MPO24 macho.

Figura 4. Receptáculo óptico y orientación del canal

INTERFAZ DE MONITOREO DE DIAGNÓSTICO (OPCIONAL)

La Función de monitoreo de Diagnóstico Digital está disponible en todos los productos QSFP DD. Una interfaz en serie de 2 cables proporciona al usuario contacto con el módulo. La estructura de la memoria se muestra en la Figura 5. El espacio de memoria está dispuesto en un espacio de dirección inferior, de una sola página, de 128 bytes y varias páginas de espacio de direcciones superiores. Esta estructura permite el acceso oportuno a las direcciones en la página inferior, por ejemplo, banderas y monitores de interrupción. Menos entradas críticas de tiempo, por ejemplo, información de ID de serie y ajustes de umbral, están disponibles con la función de selección de página. La estructura también proporciona la expansión de la dirección al agregar páginas superiores adicionales según sea necesario. La Dirección de interfaz utilizada es A0xh y se utiliza principalmente para datos críticos de tiempo, como el manejo de interrupciones, para permitir una lectura única para todos los datos relacionados con una situación de interrupción. Después de que se haya afirmado una interrupción, IntL, el host puede leer el campo de indicador para determinar el canal afectado y el tipo de indicador.

Figura 5. Mapa de memoria QSFP DD

Figura 6. Mapa de memoria baja

Figura 7. Mapa de Memoria Page 00

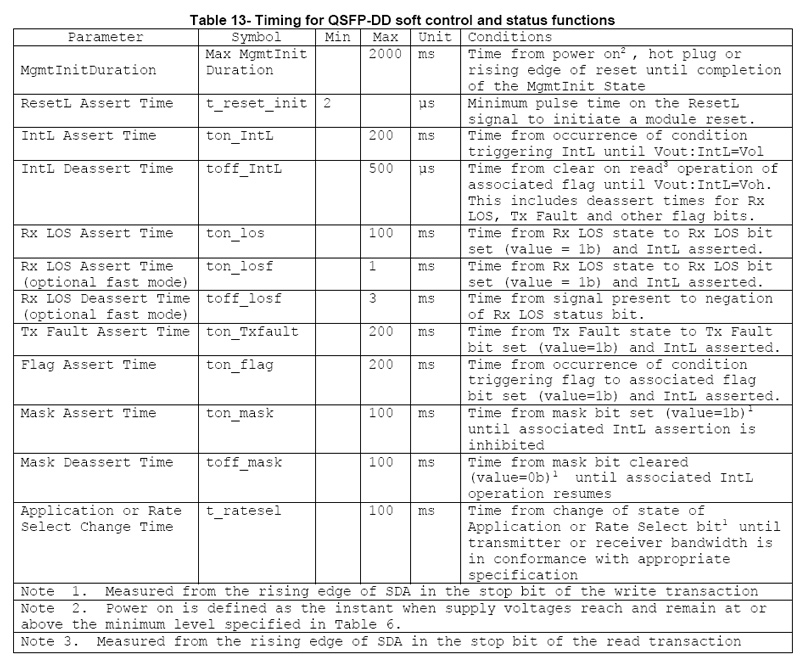

Tiempo para funciones de control suave y estado

Figura 9. Especificaciones de sincronización

Dibujo del contorno (mm)

Calificaciones máximas absolutas

Parámetro | Símbolo | Min | Máx. | Unidad |

Tensión de suministro | Vcc | -0,3 | 3,6 | V |

Voltaje de entrada | Vin | -0,3 | Vcc + 0,3 | V |

Temperatura de almacenamiento | Tst | -20 | 85 | °C |

Temperatura de funcionamiento del caso | Parte superior | 0 | 70 | °C |

Humedad (sin condensación) | Rh | 5 | 95 | % |

Condiciones de funcionamiento recomendadas

Parámetro | Símbolo | Min | Típico | Máx. | Unidad |

Suministro Voltaje | Vcc | 3,13 | 3,3 | 3,47 | V |

Funcionamiento Funda Temperatura | Tca | 0 |

| 70 | °C |

Tasa de datos Por carril | Fd |

| 25,78125 |

| Gbps |

Humedad | Rh | 5 |

| 85 | % |

Disipación de poder | PM |

|

| 4 | W |

Especificaciones eléctricas

Parámetro | Símbolo | Min | Típico | Máx. | Unidad |

Diferencial Entrada Impedancia | Zin | 90 | 100 | 110 | Ohmios |

Diferencial Salida Impedancia | Zout | 90 | 100 | 110 | Ohmios |

Diferencial Voltaje de entrada Amplitud AAmplitud | ΔVin | 300 |

| 1100 | MVp-p |

Salida diferencial Amplitud de voltaje | ΔVout | 500 |

| 800 | MVp-p |

Sesgado | Sw |

|

| 300 | PS |

Tasa de error de bits | BER |

|

| 5E-5 |

|

Lógica de entrada Alto nivel | VIH | 2,0 |

| VCC | V |

Lógica de entrada Nivel bajo | VIL | 0 |

| 0,8 | V |

Lógica de salida Alto nivel | VOH | VCC-0.5 |

| VCC | V |

Lógica de salida Nivel bajo | VOL | 0 |

| 0,4 | V |

Nota:

1. BER = 5E-5; PRBS 2 ^ 31-1@25.78125Gbps. Pre-FEC

2. La amplitud de voltaje de entrada diferencial se mide entre TxnP y TxnN.

3. La amplitud de voltaje de salida diferencial se mide entre RxnP y RxnN.

Características ópticas

Tabla 3-Características ópticas

Parámetro | Símbolo | Min | Típico | Máx. | Unidad | Notas |

Transmisor |

Longitud de onda del centro | Λc | 840 | 850 | 860 | Nm | - |

Anchura espectral RMS | Δλ | - | - | 0,6 | Nm | - |

Potencia de lanzamiento promedio, Cada carril | Paño | -8,4 | - | 2,4 | DBm | - |

Modulación óptica Amplitud (OMA), cada carril | OMA | -6,4 |

| 3 | DBm | - |

Transmisor y Ojo de dispersión Cierre (TDEC), cada carril | TDEC |

|

| 4,3 | DB |

|

Relación de extinción | ER | 3 | - | - | DB | - |

Lanzamiento promedio Poder de APAGADO Transmisor, Cada carril |

|

|

| -30 | DB | - |

Máscara para ojos Coordenadas: X1, X2, X3, Y1, Y2, Y3 | VALORES DE LA ESPECIFICACIÓN {0,3, 0,38, 0,45, 0,35, 0.41.0.5} | Relación de aciervo = 5x10-5

|

Receptor |

Longitud de onda del centro | Λc | 840 | 850 | 860 | Nm | - |

Receptor estresado Sensibilidad en OMA |

|

|

| -5,2 | DBm | 1 |

Promedio máximo Potencia en el receptor, Cada carril Entrada, cada carril |

|

|

| 2,4 | DBm | - |

Promedio Mínimo Potencia en el receptor, Cada carril

|

|

|

| -10,3 | DBm |

|

Reflectancia del receptor |

|

|

| -12 | DB | - |

LOS Assert |

| -30 |

|

| DBm | - |

LOS De-Assert - OMA |

|

|

| -7,5 | DBm | - |

LOS Histéresis |

| 0,5 |

|

| DB | - |

Nota:

1. Medido con señal de prueba de conformidad en TP3 para BER = 5E-5 por FEC

Aplicaciones

● IEEE 802.3bm 100GBASE SR4

Centro DE DATOS DE Internet

Centro DE DATOS DE Internet Preguntas frecuentes

Preguntas frecuentes Noticias de la industria

Noticias de la industria Acerca de nosotros

Acerca de nosotros Interruptor del centro de datos

Interruptor del centro de datos  Conmutador de empresa

Conmutador de empresa  Interruptor industrial

Interruptor industrial  Interruptor de acceso

Interruptor de acceso  Red integrada

Red integrada  Módulo óptico y cable

Módulo óptico y cable

Llámanos:

Llámanos:  Envíenos un correo electrónico:

Envíenos un correo electrónico:  2106B, # 3D, Cloud Park Fase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Fase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.