Características

● Velocidad de datos de hasta 28Gbps por canal

● 8 canales dúplex transmisores y receptores

● Arreglo VCSEL integrado de 850nm y matriz PD

● Sola interfaz óptica del receptáculo del conector MPO24

● Fuente de alimentación única de 3,3 V

● Función DDM implementada

● Factor de forma de QSFP-DD conectable en caliente

● Longitud máxima de enlace de 100m en fibra MPO OM4 (MMF) de 24 núcleos

● Disipación de potencia: <4,5 W

● Clase internacional 1 certificado de seguridad láser

● Rango de temperatura de funcionamiento: 0 ℃ ~ 70 ℃

● Cumple con ROHS10

Calificaciones máximas absolutas

Parámetros | Símbolo | Unidad | Min | Máx. |

Rango de temperatura de almacenamiento | Ts | ℃ | -40 | 85 |

Humedad relativa | RH | % | 5 | 95 |

Tensión de alimentación | Vcc | V | -0,5 | + 3,6 |

Condiciones de funcionamiento recomendadas

Parámetros | Símbolo | Unidad | Min. | Típico | Máx. |

Funda de funcionamiento Rango de temperatura | Tc | ℃ | 0 |

| 70 |

Tensión de alimentación | Vcc | V | 3,14 | 3,3 | 3,46 |

Tasa de bits NRZ (por canal) | BR | Gbps |

| 25,78 |

|

Características ópticas

Parámetros | Símbolo | Unidad | Min. | Típico | Máx. | Nota |

Transmisor (por carril) |

Velocidad de señalización por carril |

| Gbps | 25,78125 | NRZ |

Longitud de onda del centro |

| Nm | 840 | 850 | 860 |

|

Anchura espectral RMS | SW | Nm |

|

| 0,6 |

|

Lanzamiento promedio Potencia por carril | TXPx | DBm | -8,4 |

| 2,4 |

|

Tx OMA por carril | TxOMA | DBm | -6,4 |

| 3 |

|

Diferencia en el poder Entre Cualquier dos carriles (OMA) | DPx | DBm |

|

| 4 |

|

Potencia de lanzamiento promedio Transmisor de apagado Por carril |

| DBm |

|

| -30 |

|

Transmisor y Ojo de dispersión Cierre por carril | TDEC | DB |

|

| 4,3 |

|

El poder de lanzamiento en OMA menos TDEC |

| DBm | -7,3 |

|

|

|

Extinción óptica Relación | ER | DB | 2 |

|

|

|

Retorno óptico Tolerancia DE LA PÉRDIDA | ORL | DB |

|

| 12 |

|

Flujo rodeado | FLX | DBm | > 86% en 19um |

|

<30% a 4.5um |

|

Ruido de intensidad relativa | Rin | DB/Hz |

|

| Rin |

|

Receptor (por carril) |

Velocidad de señalización por carril |

| Gbps | 25,78125 | NRZ |

Longitud de onda del centro |

| Nm | 840 |

| 860 |

|

Umbral de daños | DT | DBm | 3,4 |

|

|

|

Recibo promedio Potencia por carril | RXPx | DBm | -10,3 |

| 2,4 |

|

Potencia del receptor (OMA) por carril | RxOMA | DBm |

|

| 3 |

|

Reflectancia del receptor | Rfl | DB |

|

| -12 |

|

Cierre de ojo vertical Penalización, por carril |

| DB |

|

| 1,9 |

|

Recibida estresada Sensibilidad (OMA) por carril | SRS | DBm |

|

| -5,2 |

|

Sensibilidad (OMA) por carril | S | DBm |

|

| -10,3 |

|

LOS Desastres | LOSD | DBm |

|

| -12 |

|

LOS Assert | LOSA | DBm | -30 |

|

|

|

LOS Histéresis |

| DBm | 0,5 |

|

|

|

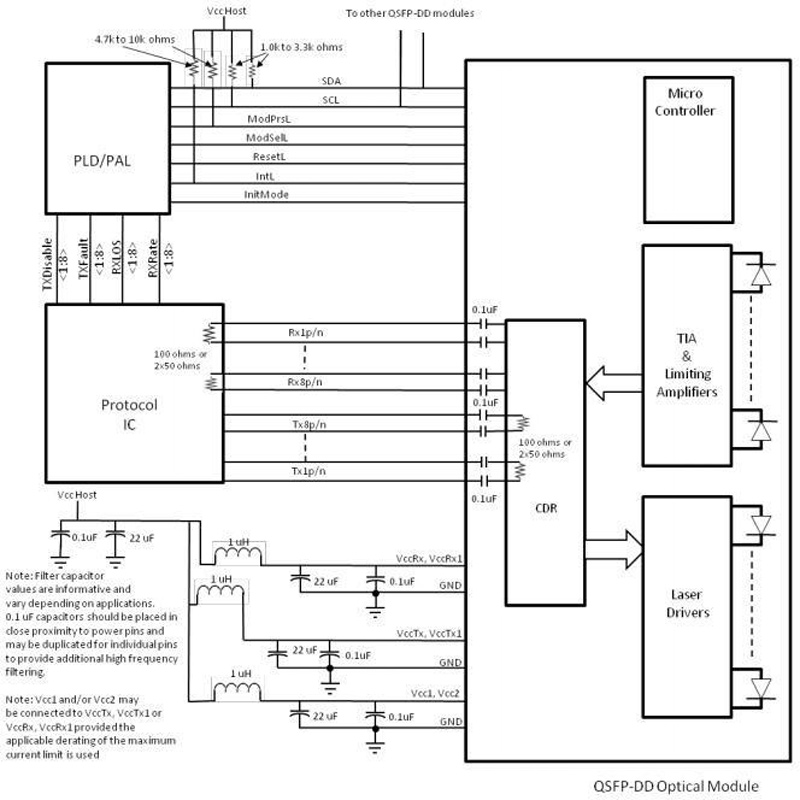

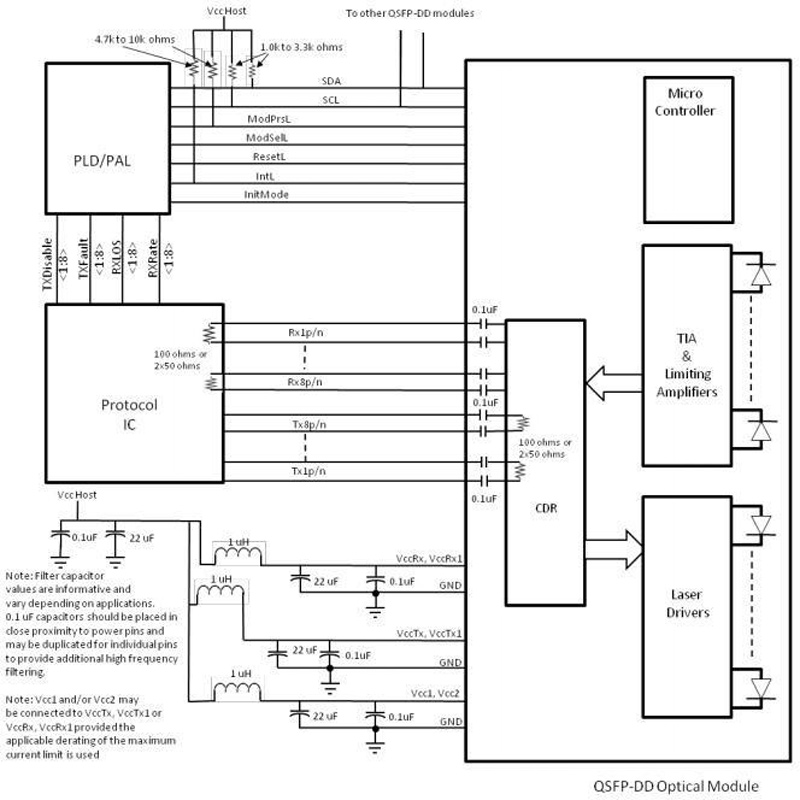

Principio Diagrama

Figura 1. Diagrama del principio del módulo

Definición de puertos eléctricos

Parámetros | Símbolo | Unidad | Min. | Típico | Máx. | Nota |

Tensión de suministro | VCC VCC3.3-Tx VCC3.3-Rx | V | 3,14 | 3,3 | 3,46 |

|

Corriente de suministro | Icc | MA |

|

| 1300 |

|

Consumo de energía | PC | W |

|

| 4,5 |

|

Transceptor Encendido Inicializar el tiempo |

| MS |

|

| 2000 |

|

Transmisor |

Entrada de un solo final VoltageTolerancia | VinT | V | -0,3 |

| 4,0 |

|

Datos diferenciales Columpio de entrada |

VIN |

MVp-p |

300 |

|

1200 |

|

AC Común Modo de salida Voltaje (RMS) |

| MV | 15 |

|

|

|

Entrada diferencial Impedancia |

| VD | 90 | 100 | 110 |

|

Receptor |

Entrada de un solo final VoltageTolerancia | VoutR | V |

|

| 0,2 |

|

Datos diferenciales Columpio de salida | Vout,PP | MVp-p | 350 |

| 850 |

|

Modo común AC Voltaje de salida (RMS) |

| MV |

|

| 7,5 |

|

Salida diferencial Impedancia |

| VD | 90 | 100 | 110 |

|

Comunicación IIC |

Frecuencia de reloj IIC |

| KHZ |

| 100 | 400 |

|

Reloj de estiramiento |

| Nosotros |

|

| 500 |

|

Tiempo de retención de datos |

| NS | 300 |

|

|

|

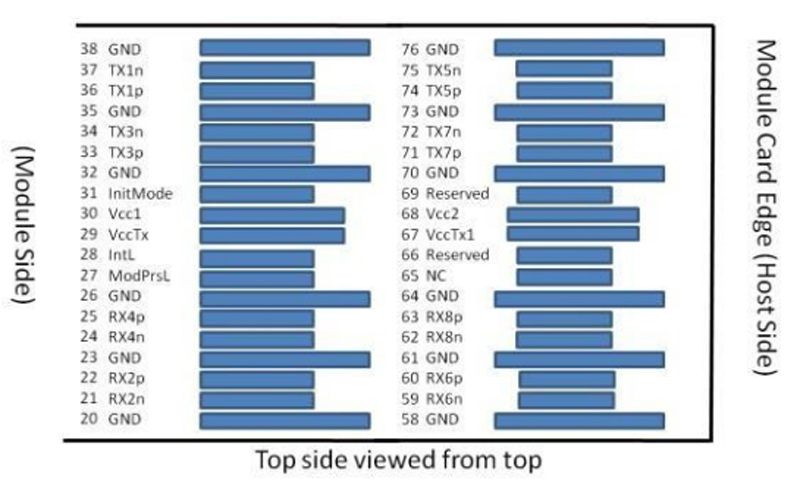

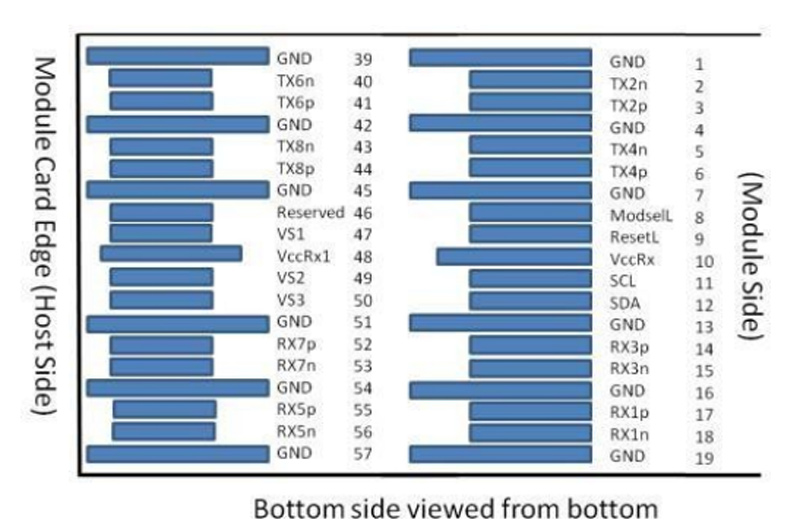

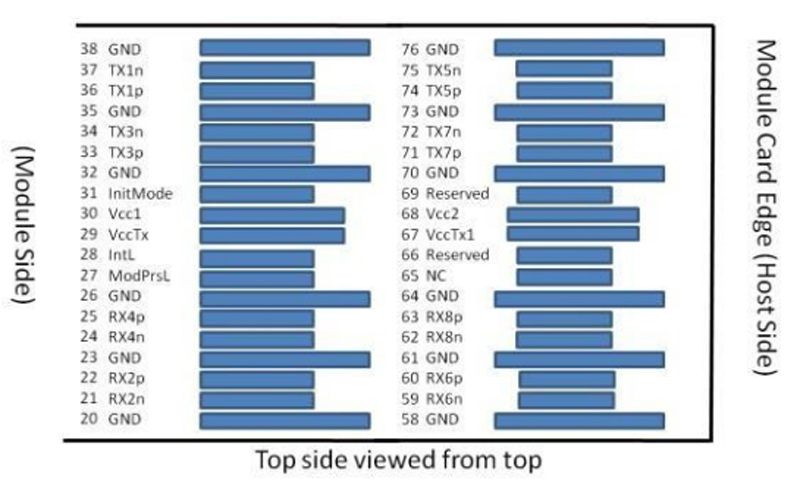

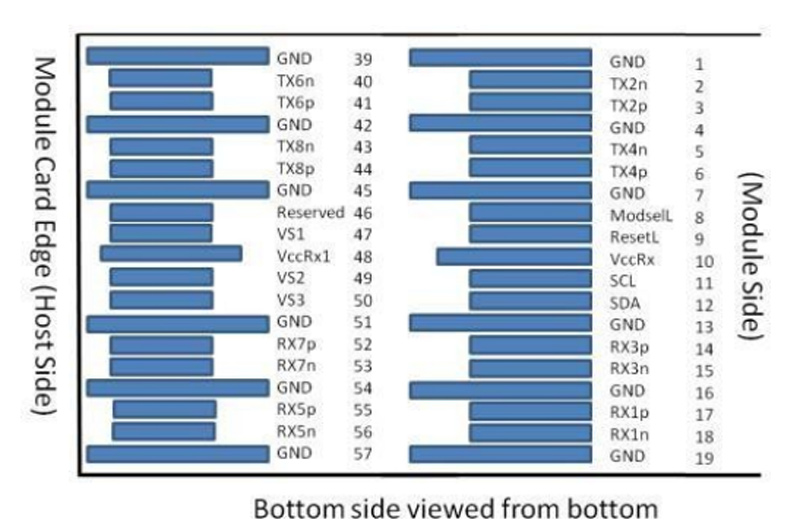

Pin Deion

Figura 2. Detalles de la salida eléctrica

Pin | Lógica | Símbolo | Deion | Nota |

1 |

| GND | Terreno | 1 |

2 | CML-I | Tx2n | TransmisterInverteDataInput |

|

3 | CML-I | Tx2p | TransmisterNon-InverteDataInput |

|

4 |

| GND | Terreno | 1 |

5 | CML-I | Tx4n | TransmisterInverteDataInput |

|

6 | CML-I | Tx4p | TransmisterNon-InverteDataInput |

|

7 |

| GND | Terreno | 1 |

8 | LVTTL-I | ModSelL | ModuloSelect |

|

9 | LVTTL-I | ResetL | Moduloreset |

|

10 |

| VccRx | 3,3 VPowerSupplyReceptor | 2 |

11 | LVCOMS-I/O | SCL | 2-WireSerialInterfaceClock |

|

12 | LVCOMS-I/O | SDA | 2-WireSerialInterfaceData |

|

13 |

| GND | Terreno | 1 |

14 | CML-0 | Rx3p | ReceiverNon-InvertedDataOutput |

|

15 | CML-0 | Rx3n | ReceiverInvertidDataOutput |

|

16 |

| GND | Terreno | 1 |

17 | CML-0 | Rx1p | ReceiverNon-InvertedDataOutput |

|

18 | CML-0 | Rx1n | ReceiverInvertidDataOutput |

|

19 |

| GND | Terreno | 1 |

20 |

| GND | Terreno | 1 |

21 | CML-0 | Rx2n | ReceiverInvertidDataOutput |

|

22 | CML-0 | Rx2p | ReceiverNon-InvertedDataOutput |

|

23 |

| GND | Terreno | 1 |

24 | CML-0 | Rx4n | ReceiverInvertidDataOutput |

|

25 | CML-0 | Rx4p | ReceiverNon-InvertedDataOutput |

|

26 |

| GND | Terreno | 1 |

27 | LVTTL-0 | ModPrsL | ModulePresente |

|

28 | LVTTL-0 | Intl | Interrupción |

|

29 |

| Vcctx | 3,3 VPowerSupplytransmisor | 2 |

30 |

| VCC1 | 3,3 VPowerSupply | 2 |

31 | LVTTL-I | Modo de entrada | Modo de inicialización; En legacyQSFPapplications,theIntiModepadisc AlledLPMode |

|

32 |

| GND |

Terreno | 1 |

33 | CML-I | Tx3p | TransmisterNon-InverteDataInput |

|

34 | CML-I | Tx3n | TransmisterInverteDataInput |

|

35 |

| GND | Terreno | 1 |

36 | CML-I | Tx1p | TransmisterNon-InverteDataInput |

|

37 | CML-I | Tx1n | TransmisterInverteDataInput |

|

38 |

| GND | Terreno | 1 |

39 |

| GND | Terreno | 1 |

40 | CML-I | Tx6n | TransmisterInverteDataInput |

|

41 | CML-I | Tx6p | TransmisterNon-InverteDataInput |

|

42 |

| GND | Terreno | 1 |

43 | CML-I | Tx8n | TransmisterInverteDataInput |

|

44 | CML-I | Tx8p | TransmisterNon-InverteDataInput |

|

45 |

| GND | Terreno | 1 |

46 |

| Reservado | Forfutureuse | 3 |

47 |

| VS1 | ModuleVendorSpecific1 | 3 |

48 |

| VccRx1 | 3,3 VPowerSupplyReceptor | 2 |

49 |

| VS2 | ModuleVendorSpecific2 | 3 |

50 |

| VS3 | ModuleVendorEspecific3 | 3 |

51 |

| GND | Terreno | 1 |

52 | CML-0 | Rx7p | ReceiverNon-InvertedDataOutput |

|

53 | CML-0 | Rx7n | ReceiverInvertidDataOutput |

|

54 |

| GND | Terreno | 1 |

55 | CML-0 | Rx5p | ReceiverNon-InvertedDataOutput |

|

56 | CML-0 | Rx5n | ReceiverInvertidDataOutput |

|

57 |

| GND | Terreno | 1 |

58 |

| GND | Terreno | 1 |

59 | CML-0 | Rx6n | ReceiverInvertidDataOutput |

|

60 | CML-0 | Rx6p | ReceiverNon-InvertedDataOutput |

|

61 |

| GND | Terreno | 1 |

62 | CML-0 | Rx8n | ReceiverInvertidDataOutput |

|

63 | CML-0 | Rx8p | ReceiverNon-InvertedDataOutput |

|

64 |

| GND | Terreno | 1 |

65 |

| NC | NotConnect | 3 |

66 |

| Reservado | Forfutureuse | 3 |

67 |

| VccTx1 | 3,3 VPowerSupplytransmisor | 2 |

68 |

| VCC2 | 3,3 VPowerSupply | 2 |

70 |

| GND | Terreno | 1 |

71 | CML-I | Tx7p | TransmisterNon-InverteDataInput |

|

72 | CML-I | Tx7n | TransmisterInverteDataInput |

|

73 |

| GND | Terreno | 1 |

74 | CML-I | Tx5p | TransmisterNon-InverteDataInput |

|

75 | CML-I | Tx5n | TransmisterInverteDataInput |

|

76 |

| GND | Terreno | 1 |

Notas:

1.QSFP-DD utiliza un terreno común (GND) para todas las señales y el suministro (energía). Todo el común dentro del módulo de QSFP-DD y todas las tensiones de módulo están referenciadas a este potencial a menos que se indique lo contrario. Las tesis conectadas directamente a La placa central señalan un plano terrestre común.

2.VccRx, VccRx1, Vcc1, Vcc2, VccTx y VccTx1 se aplicarán simultáneamente. Los requisitos definidos para el lado del host del conector de borde de la tarjeta host se enumeran en la Tabla 4. VccRx, VccRx1, Vcc1, Vcc2, VccTx y VccTx1 pueden conectarse internamente dentro del módulo en cualquier combinación. Los pines Vcc del conector están clasificados para una corriente máxima de 1000mA.

3. Todos los pines específicos del proveedor, reservados y sin conexión se pueden terminar con 50 ohmios para el suelo en el host. La almohadilla 65 (sin conexión) se dejará sin conexión dentro del módulo. Las almohadillas reservadas y específicas del proveedor deberán tener una impedancia a GND superior a 10 kOhms y inferior a 100pF.

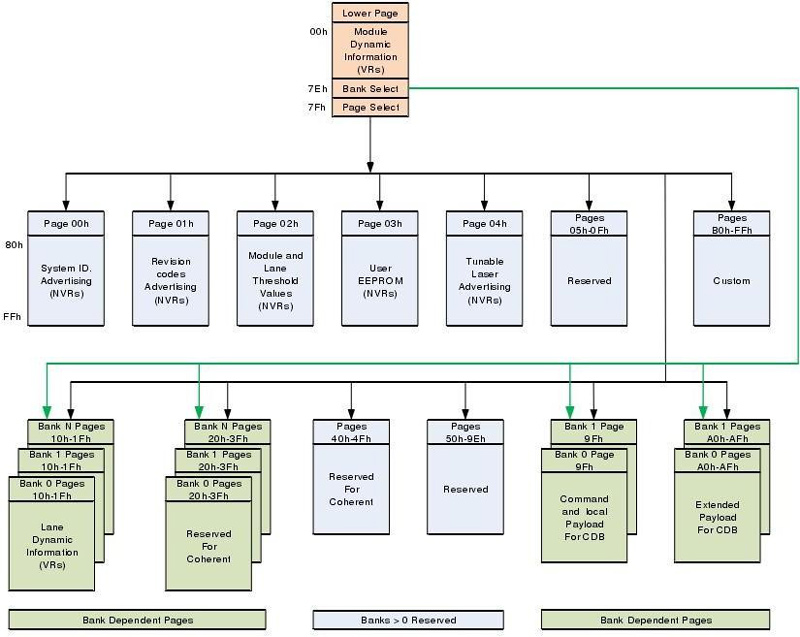

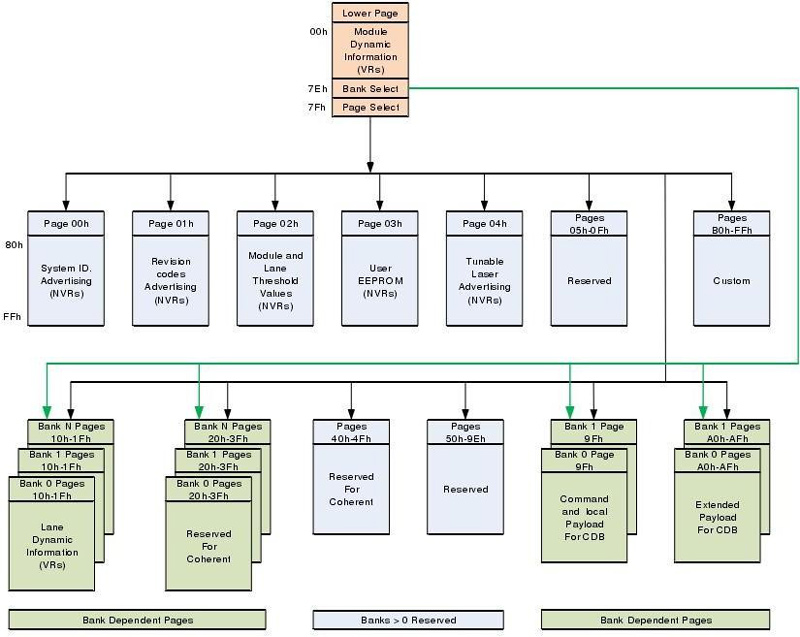

Mapa de memoria de Diagnóstico Digital

Figura 3 mapa de memoria de Diagnóstico Digital

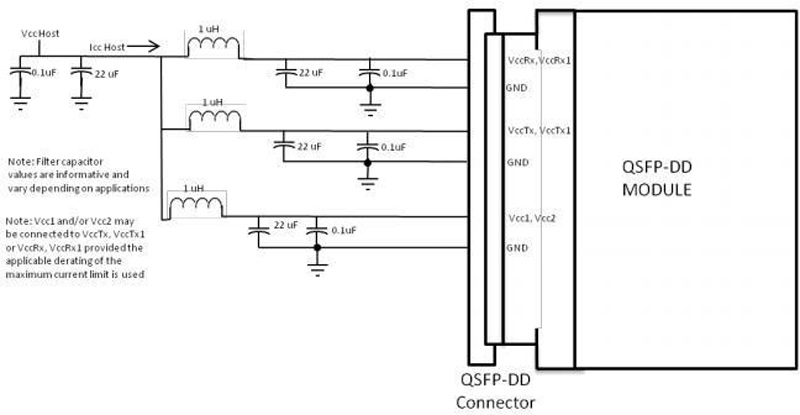

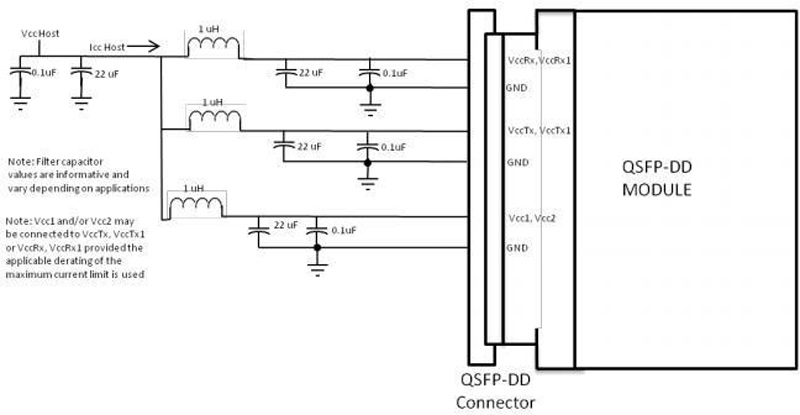

Filtrado de fuente de alimentación de la placa host

Cualquier caída de voltaje a través de una red de filtro en el host se cuenta con la especificación de precisión del punto de ajuste DC del host. Se deben utilizar inductores con resistencia CC de menos de 0,1 ohm para mantener el voltaje requerido en el conector de la tarjeta de borde del host. La figura es la interfaz de transceptor/host sugerida.

Figura 4 Filtrado recomendado de fuente de alimentación de la placa host

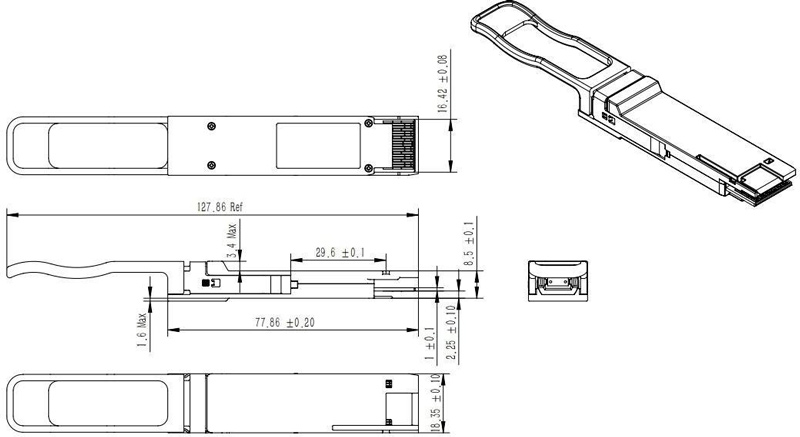

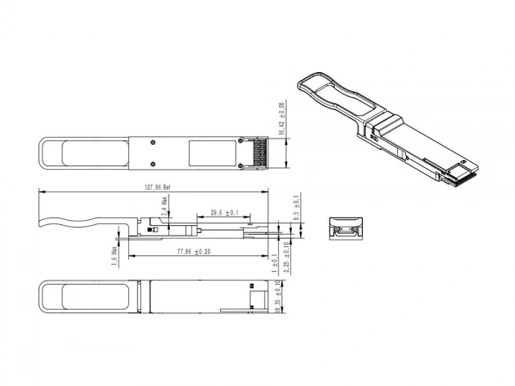

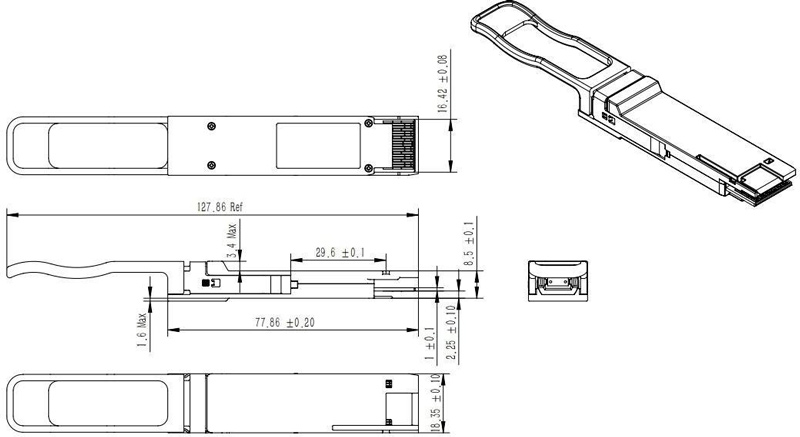

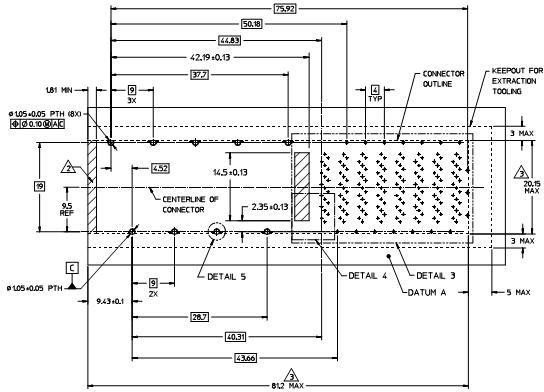

Dibujo del contorno (mm)

Figura 5 Esquema del paquete

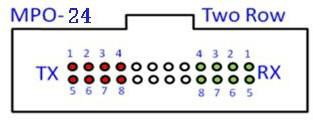

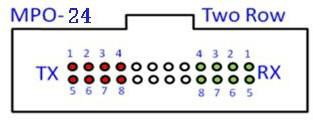

Figura 6 MPO Diagrama de pinout y Deion

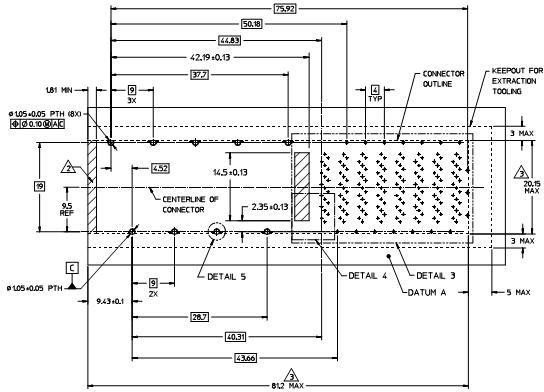

Recomendación de diseño de PCB de host

Figura 7 Recomendación de diseño de PCB

Aplicaciones

● Ethernet 200GBASE-SR8

● Ethernet 2 × 100GBASE-SR4

● Conexiones de conmutador y enrutador

● Centros de datos

● Otros requisitos de interconexión 200G

Centro DE DATOS DE Internet

Centro DE DATOS DE Internet Preguntas frecuentes

Preguntas frecuentes Noticias de la industria

Noticias de la industria Acerca de nosotros

Acerca de nosotros Interruptor del centro de datos

Interruptor del centro de datos  Conmutador de empresa

Conmutador de empresa  Interruptor industrial

Interruptor industrial  Interruptor de acceso

Interruptor de acceso  Red integrada

Red integrada  Módulo óptico y cable

Módulo óptico y cable

Llámanos:

Llámanos:  Envíenos un correo electrónico:

Envíenos un correo electrónico:  2106B, # 3D, Cloud Park Fase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, # 3D, Cloud Park Fase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.